www.edn-europe.com Issue 5

Hybrid execution - the next step in hardware-software co-development – page 12 Top free DIY tools every engineer needs – page 14 Understanding efficiency: looking for the worst-case scenario – page 15 Bandpass filter, adjustable Q, constant maximum gain, with two op-amps – page 16 Designing for the Internet of Things: part IV, The Cloud – page 18 Ensuring digital displays flourish in all conditions – page 19

# contents

**JUNE 2014**

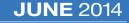

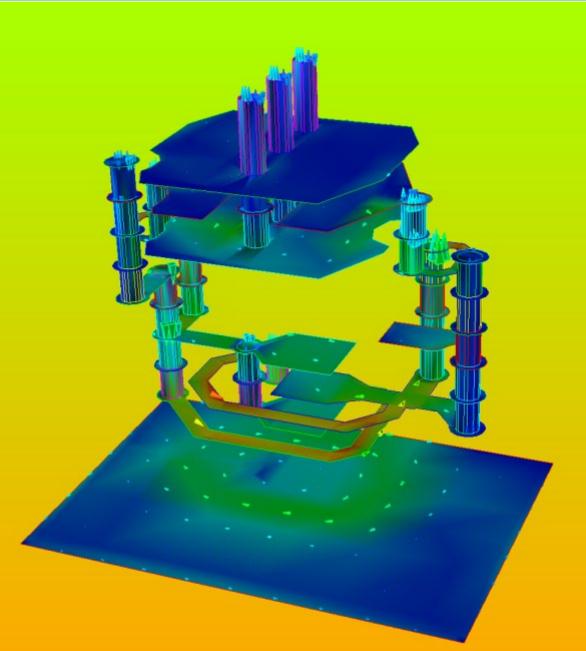

#### **Cover image; Modulated RF analysis**

The image on this month's cover is taken from a screen shot illustrating the capabilities of Agilent Technologies EEsof's Genesys EDA software, 2014 release. This release features modulated RF analysis as well as enhancements to its

custom-filter direct synthesis technology and, as depicted by the illustration, spans extraction from physical interconnect and layout, through to performance analysis of complete digital **RF systems. Using** Genesys 2014, designers can simulate digitally modulated RF

signals such as those found in today's defence and consumer wireless applications as easily as they do traditional analogue RF signals. The software delivers system budget analysis of these digital modulation metrics for every component in the system block diagram, all in a single pass. Underlying Genesys 2014's accurate digital modulation analysis is a new, embedded numeric dataflow simulator that also enables easy verification against

dataflow simulator that also enables easy verification against the latest wireless standards for WLAN 802.11ac and LTE-3GPP. Click right for more details.

## **FEATUREARTICLES**

#### 12

Hybrid execution - the next step in the evolution of hardware-software codevelopment by Frank Schirrmeister, Cadence Design Systems

#### 14

Top free DIY tools every engineer needs by Cabe Atwell

#### 15

Understanding efficiency: looking for the worst-case scenario by Peter Blyth, XP Power

#### 16

Bandpass filter, adjustable Q, constant maximum gain, with two op-amps by Nazafat Ullah Khan

#### 18

Designing for the Internet of Things: part IV, The Cloud by Christian Legare, Micrium

#### 19

Ensuring digital displays flourish in all conditions by Mike Logan, andersDX

### EDN. COMMENT

4 Heartbleed: the wakeup call the open-source community needed? By Brian Dipert

#### Analog Tips

13 Simple RC network reduces LDO noise

by Glenn Morita, Analog Devices

### MECHATRONICS

20 Control, control, you must learn control!

#### TALES FROM THE CUBE

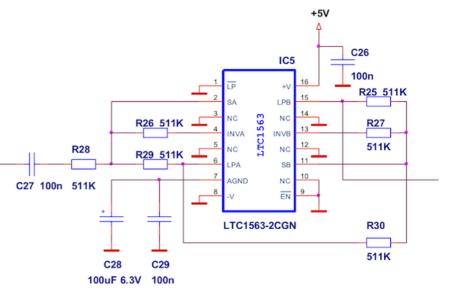

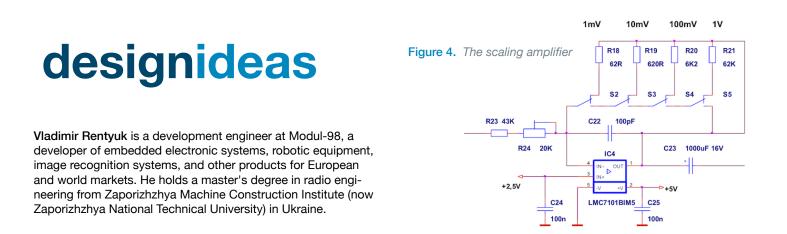

28 Don't send a man to do a meter's job. by Vladimir Rentyuk

#### productroundup

28 Power chips and modules; Wireless modules for Bluetooth & USB; FORTH language revisited

### DESIGNIDEAS

- 21 Versatile noise generator tests signal recovery gear

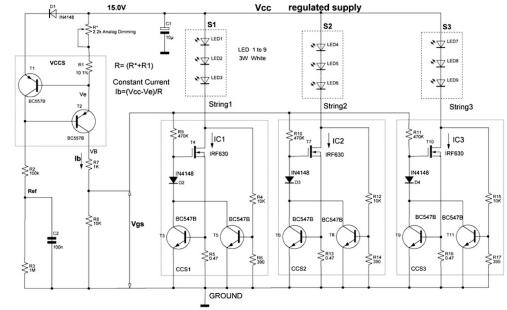

- 22 Failsafe multichip LED module driver

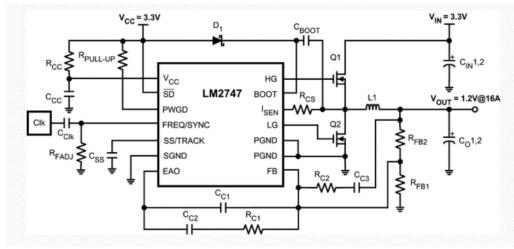

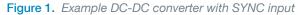

- 23 Avoid problems with multiple DC-DC converters

# p<mark>u</mark>lse

- 6 AMD renews R series embedded APUs with HSA designs

- 7 100V, normally-off, GaN transistors in low inductance, thermallyefficient packaging

- 8 Low-cost web-based EDA/PCB software from Mentor & Digi-Key

- 8 Integrated, nanopower magnetoresistive sensors offer new detection options

- 9 Panasonic's MCUs with resistive RAM, in distribution

- 9 10-A backup power controller manages supercapacitor stacks

- 10 Reference design outputs 4 analogue variables, cuts component count

- 11 14-bit, 2 Gsample/sec converters boost performance, ease of use

#### **JUNE** 2014

www.edn-europe.com Issue 5

europe

#### CONTACTS

PUBLISHER André Rousselot +32 27400053 andre.rousselot@eetimes.be

EDITOR-IN-CHIEF Graham Prophet +44 7733 457432 edn-editor@eetimes.be

Patrick Mannion Brand Director EDN Worldwide CIRCULATION & FINANCE Luc Desimpel luc.desimpel@eetimes.be

#### ADVERTISING PRODUCTION & REPRINTS

Lydia Gijsegom lydia.gijsegom@eetimes.be

ART MANAGER Jean-Paul Speliers

ACCOUNTING Ricardo Pinto Ferreira

#### **EUROPEAN BUSINESS PRESS SA**

7 Avenue Reine Astrid 1310 La Hulpe Tel: +32 (0)2 740 00 50 Fax: +32 (0)2 740 00 59 www.electronics-eetimes.com VAT Registration: BE 461.357.437 RPM: Nivelles Company Number: 0461357437

© 2014 E.B.P. SA

EDN-EUROPE is published 11 times in 2014 by European Business Press SA, 7 Avenue Reine Astrid, 1310 La Hulpe, Belgium Tel: +32-2-740 00 50 Fax: +32-2-740 00 59 email: info@eetimes.be. VAT Registration: BE 461.357.437. RPM: Nivelles. It is is free to qualified engineers and managers involved in engineering decisions – see: http://www.edn-europe.com/subscribe Copyright 2014 by European Business Press SA. All rights reserved.

#### SALES CONTACTS

#### **Europe**

Daniel Cardon France, Spain, Portugal +33 688 27 06 35 cardon.d@gmail.com

Nadia Liefsoens Belgium +32-11-224 397 n.liefsoens@fivemedia.be

Nick Walker UK, Ireland, Israel, The Netherlands +44 (0) 1442 864191 nickjwalker@btinternet.com

Victoria & Norbert Hufmann Germany, Austria, Eastern Europe +49 911 93 97 64 42 sales@hufmann.info

Monika Ailinger Switzerland +41-41-850 4424 m.ailinger@marcomedia.ch

Andrea Rancati Italy +39-02-284 6716 info@silvera.it

Colm Barry & Jeff Draycott Scandinavia +46-40-41 41 78 jeff.draycott@womp-int.com colm.barry@telia.com

#### **USA & Canada**

Todd A. Bria West +1 831 477 2075 tbria@globalmediasales.com

Jim Lees PA, NJ & NY +1-610-626 0540 jim@leesmedia.com

Steve Priessman East, Midwest, South Central & Canada +1-630-420 8744 steve@stevenpriessman.com

Lesley Harmoning East, Midwest, South Central & Canada +1-218.686.6438 lesleyharmoning@gmail.com

#### Asia

Keita Sato Japan +81-3-6824-9386 Mlshida@mx.itmedia.co.jp

Grace Wu Asian Sources Publications Asia (886-2) 2712-6877 wuq@globalsources.com

John Ng Asian Sources Publications Asia (86-755) 8828 – 2656 jng@globalsources.com EDN. COMMENT

# HEARTBLEED: THE WAKEUP CALL THE OPEN-SOURCE COMMUNITY NEEDED?

#### by Brian Dipert, writing for EDN

When the "Heartbleed" vulnerability in OpenSSL had just become public and looked as if it would have widespread effects, my immediate reaction was, "Heartbleed is big, bad, and recent enough that it justifies a column all its own." This is indeed that column. However, although I'll provide a brief background on Heartbleed's cause, effects, and in-progress fixes, plenty of other already-published literature already covers this same ground more extensively than I plan to. My particular angle on this topic is somewhat different, as you may already be able to tell from this post's title. If you need a refresh on SSL and OpenSSL, Wikipedia provides a suitable summary.

So what's Heartbleed? Wikipedia to the rescue again: "Heartbleed is a security bug in the open-source OpenSSL cryptography library, which is widely used to implement the Internet's Transport Layer Security (TLS) protocol. Heartbleed results from improper input validation (due to a missing bounds check) in the implementation of the Transport Layer Security (TLS) heartbeat extension, the heartbeat being behind the bug's name. This vulnerability is classified as a buffer over-read.

The "heartbeat extension" is a critical piece of the puzzle. It's in effect an SSL-specific (and optional) implementation of the more general "ping" function, intended to enable a client system to discern that a server on the other end of the SSL connection is still present".

As an as-usual-excellent XKCD web comic concisely points out, the OpenSSL bug enables a heartbeat-initiating client to coax a server into engorging more information than intended. This information can potentially be nothing more than garbage ... or it could be registered users' account logins and passwords, for example. It was initially believed that private server RSA keys used to generate certificates might be safe, but that theory was unfortunately debunked quickly. And although the flaw has now been patched, the number of affected systems and software packages is vast, and they aren't necessarily easy to update (that is, if they ever get updated at all).

How did the OpenSSL mess happen in the first place? To understand the answer to this question, I'll first quote from a prior open source-themed post of mine, published in October 2012: "Most open-source efforts are maintained by one or a handful of developers and 'supported' by a rag-tag band of enthusiasts, all of whom do so on the side by virtue of their (other) paying 'day jobs'."

You might think that OpenSSL, by virtue of its ubiquity, would be a well-funded exception to this rule. You'd think wrong (although the funding situation thankfully seems to be changing). As it turns out, Stephen Henson was the only full-time OpenSSL developer, and he's by no means living in the lap of luxury. The flaw was actually created by one of a short list of part-time contributors, Robin Seggelmann, made it through Henson's review undetected, and survived in the code base for more than two years before being discovered.

Open-source software has some compelling selling points. For one thing, it's free, and the many thousands of developer eyeballs peering over it generally result in robust code.

So what about all those eyeballs, developer and implementer alike? Why didn't they catch it? Back to the BuzzFeed writeup I mentioned earlier for the explanation:

"This stems in part from how its current funding structure affects its priorities: For now, OpenSSL's development lives and dies by the OSF's commercial income, almost all of which comes from putting in new features, rather than maintaining the old. The current setup means, [OpenSSL foundation organiser] Steve Marquess readily admits, that "the fundamentals of OpenSSL are being neglected. No one is hiring us to maintain the current code base." And of course mistakes can happen. When they do, there currently isn't the money to pay a person, never mind a team, to go through the 456,332 lines of [C] source code with a fine-tooth comb to find them.

There are plenty of people looking at the OpenSSL code, including Professor Paterson, whose Information Security Group (ISG) at Royal Holloway is incentivised by the University of London to conduct research into OpenSSL and to spot bugs. But Paterson points out that there are significantly fewer people writing the code within the OpenSSL project than those on the outside looking in, scanning it for weaknesses — and the former are adding more stuff in, not taking stuff out and cleaning up the contradictions contained within the code base. The code has tripled in size from late 1998 and early 1999 when SSLeay became OpenSSL; on average 1,575 new lines of code have been added each month for the past 15 years.

And of course, among those thousands of eyeballs are sets with more nefarious objectives in mind, and access to source code enables them to develop exploits for unpatched, easily identified software builds.

This situation leaves me with an unanswered question that I've long pondered (and that others are now asking, as well); is open source fundamentally better than closed source? A closed-source equivalent to OpenSSL very well might exhibit the same Achilles Heel, but keep in mind that this bug wasn't discovered by source code perusal but by usage experimentation, which resulted in no fundamental benefit for open versus closed source. The ability to analyse open source code to identify and fix bugs is counterbalanced by the opportunity to exploit them, particularly when vulnerabilities are revealed before fixes are even in place. And although some folks object to the "monopoly" supply of closed-source code, OpenSSL highlights that open source software is no less single-sourced in many cases.

In March 2007 I wrote the following, which is eerily prescient in light of the Heartbleed situation:

"Open source or closed source? I really don't care, particularly if the manufacturer has used open source as a means of bolstering its profit margin versus enabling it to lower the product price versus a closed source alternative. And if the closed source product is more maintainable (assuming, of course, that the product is inherently vulnerable to potential code flaws .... a fair bet in this increasingly network-connected world of technology), I'll vote for closed source with my wallet.

# Keep abreast of the latest industry news with our newsletters

www.electronics-eetimes.com/newsletters

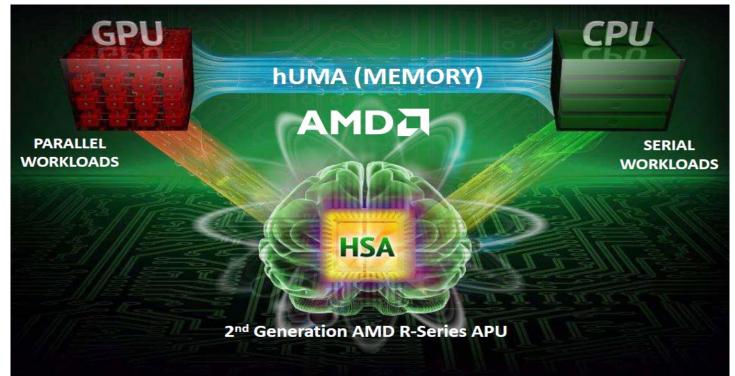

### AMD renews R series embedded APUs with HSA designs

MD has introduced a second generation of its "R" series APU (combined CPU and graphics processing unit) for the embedded market, in 28-nm technology and with an implementation of the HSA (hetergeneous system architecture) to increase processing throughput.

The HSA aims to "unlock the GPU for embedded computing". The many-core structure of the GPU has been available to embedded designers for some time, using the "GPGPU" approach – general purpose [computing using] the GPU. Previously, the GPU operated as a slave to the CPU, with tasks – that the programmer identified as having parallel attributes – for the ingly and that while knowledge of, for example, OpenCL will continue to be useful in programming the chips, the objective is to open up the power of the product range to design teams that are not heavily graphics-oriented. "Think serial/parallel rather than CPU/graphics," he added, also noting that there are many networking tasks that exhibit a high degree of parallelism. You will be able to include C++ code in a mixed-compilation flow and create a parallel implementation.

The second generation embedded R-series Accelerated Processing Unit (APU) (codenamed "Bald Eagle") has multiple (up to four) x86 cores plus GPU; it supports 4k graphics and up to

GPU queued for it by the CPU, and each has its own memory space. In the HSA implementation the two cores have equal status, and can work together in a shared memory space. "Multiple compute tasks can work on the same coherent memory regions, utilizing barriers and atomic memory operations as needed to maintain data synchronization (just as multi-core CPUs do today)," - as AMD puts it. The program flow can move tasks – parallel or serial – to the most appropriate processing element, and the task does not have to move from memory space to memory space.

Asked about the implications for programming, an AMD spokesman said that code tool support will be updated accord-

four separate displays. Alongside AMD's "Steamroller" CPU architecture is the AMD Radeon HD 9000-series GPU architecture that supports Microsoft DirectX 11.1, OpenGL 4.2 and OpenCL all within a 35W power envelope. (35W is for the quad-core version; a dual-x86-core device will have a 17W power envelope.)

The second generation embedded R-series APUs support Microsoft Windows and Linux, with Microsoft DirectX 11.1 and OpenGL 4.3 supported, along with OpenCL, giving develop-

ers access to computation power of the Radeon HD 9000-series GPU. This means whether applications run on Windows or Linux, R-series APUs will run them.

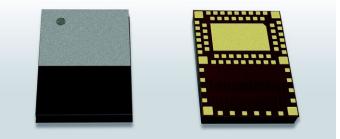

# 100V, normally-off, GaN transistors in low inductance, thermally-efficient packaging

aN Systems has announced a family of normally-off 100V gallium nitride – GaN – transistors that spans 20-80A with very low on-resistance and total gate charge. The company contends that GaN represents such a step change in electrical performance that conventional package formats negate the benefits, and has designed its own

easy-to-mount package format that has extremely low resistance and inductance.

GS61002P, GS61004P, GS61006P and GS61008P are respectively 20A/21 m $\Omega$ , 40A/11 m $\Omega$ , 60A/8 m $\Omega$  and 80A/5 m $\Omega$  parts while GS71008P is an 80A/5 m $\Omega$  half bridge

device. These enhancement mode parts feature a reverse current capability, source-sense for optimal high speed design and exceptionally low Total Gate Charge ( $Q_{\rm G}$ ) and Reverse Recovery Charge ( $Q_{\rm RR}$ ). RoHS compliant, the devices are delivered in GaN Systems' near chipscale, embedded GaNPX package which minimises inductance and optimises thermal performance. GaN Systems' Island Technology addresses cost, performance,

and manufacturability challenges of gallium nitride resulting in devices that are smaller and more efficient than traditional design approaches; larger devices are built with multiple isolated "island" transistor elements, and redundancy allows the company to overcome some inherent limitations of working in the GaN material. The package it employs on these transistors uses

> a built-up layer structure of conventional PCB material, with multiple vias providing a very short and low-inductance path from the top of the die back to the pads of the package.

Girvan Patterson, President of GaN Systems comments that to view a GaN transistor as a silicon replace-

ment with a better parameter set is to miss the point; the electrical performance at device level can be so much better that a complete new design approach is needed to

get the most out of the devices – and that all of the elements of such an approach are now in place.

G56100

# Honeywell

Magnetoresistive Sensor ICs, Nanopower Series

### High sensitivity. Extremely low power.

### Low-cost web-based EDA/PCB software from Mentor & Digi-Key

istributor Digi-Key, and Mentor Graphics, have configured a design tool, described as "concept-to-prototype", aimed at individual designers and intended to support "green-field" projects before transition to production. A Beta version of the package, which will be priced below \$300, is now available from Digi-Key.

Designer Schematic addresses (the two companies say) escalating demand from professional engineers for EDA software at an affordable price point for new R&D projects, while facilitating access to the latest parts. "Innovators ... need to have access to professional-class PCB design tools to easily capture their design concepts. Mentor Graphics' partnership with Digi-Key provides an opportunity to deliver our proven design technologies to individual engineers at very attractive price points," said Henry Potts, vice president and general manager of Mentor Graphics Systems Design Division, adding, "... Mentor Graphics is extending its range of PCB development solutions [to serve] individual engineers working on conceptual projects, [in addition to] the desktop market with PADS, and the extended enterprise with Xpedition."

The Designer Schematic tool is scheduled to launch early this

summer, at a sub-\$300 price point. Engineers will access firstclass design tools, and use new components with error-free EDA representation, as they are released, providing direct paths to quick-turn PCB layout and manufacturing services. The

web-based software is designed to give engineers real-time access to the latest design components along with easy, errorfree access to Design Service Providers and PCB Fabrication and Manufacturing Services.

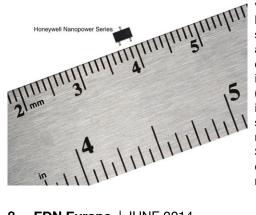

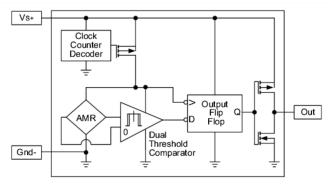

# Integrated, nanopower magnetoresistive sensors offer new detection options

oneywell has introduced a nanopower anisotropic magnetoresistive sensor IC; the technology provides position detection based on magnetic field sensing, using a very small and low-cost package, with on-chip integration of level detection and switching to give a simple on/off output and to replace reed switches where they are still the only option.

The device's high sensitivity, Honeywell says, allows you to cut costs, and to use the sensors in battery operated equipment with extremely low power requirements, where the solid state, non-contact design provides a reliable, durable alternative to reed switches.

The Nanopower Anisotropic Magnetoresistive Sensor ICs pro-

vide the highest level of magnetic sensitivity (as low as 7 Gauss typical) while requiring nanopower (360 nA average, in a typical reedswitch-replacement application). Smaller and more durable and reliable than reed switches, at the same sensitivity and essentially the same cost, the new sensor ICs can be deployed where previously only reed switches could be used for reasons of low power requirements and large air gap needs. The 360 nA figure is based on a 0.015% duty cycle of typically 15  $\mu$ sec wake/100 msec sleep cycle.

Response time is not specified in the initial data sheet; the 100 msec cycle appears chosen to match the requirements of a typical reed-switch application, detecting whether or not (say) a door is open or closed, within 1/10th of a second. The 15  $\mu$ sec on-time implies an actual detection in single-figures- $\mu$ secs, which could support detection of events at up to (perhaps) around 100 kHz – at the cost of running the device at its on-state current, which is 1 mA typical – sleep current is 160 to 260 nA over the supply voltage range.

These ICs' higher sensitivity can function over air gaps twice the distance that Hall-effect sensors can accommodate. The higher sensitivity improves design flexibility and can offer significant application cost savings by utilising smaller or lower strength magnets.

"Due to the significant price increases for rare earth magnets, design engineers using Hall-effect sensors have been looking for ways to decrease the total cost of design by using less magnetic material, or moving to a more common magnet in their applications," said Josh Edberg, senior product marketing

manager for Honeywell Sensing and Control. The Nanopower Series is available in two magnetic sensitivities: Ultra-high sensitivity SM351LT: 7 Gauss typical operate, 11 Gauss maximum operate, very low cur-

rent draw (360 nA typical); Very high sensitivity SM353LT: 14 Gauss typical operate, 20 Gauss maximum operate, very low current draw (310 nA typical). The sensors operate from 1.65 to 5.5V.

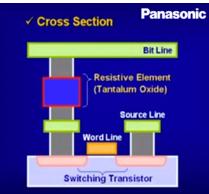

### Panasonic's MCUs with resistive RAM, in distribution

Mouser Electronics has the MN101L 8-bit Microcontrollers from Panasonic, the first microcontrollers with internal Resistive RAM (ReRAM). Resistive RAM is a new non-volatile embed-

ded memory that offers five times the write performance of Flash or EEPROM memory without the need for an erase cycle. This has the benefit of offering high-speed nonvolatile writing and longer operational times in battery powered devices.

Panasonic's Resistive RAM is based on a cell structure where a binary "1" and "0" is read based on the resistance of a thin-film metal oxide (tantalum oxide) sandwiched between two electrodes on the top and bottom of the metal oxide. The state of the memory cell is changed to a "1" by

applying a pulsed negative voltage to the top electrode. This causes oxygen ions to migrate into the tantalum oxide, lowering the resistance and making the cell conductive to electricity. The state of the cell is changed to a "0" by applying a pulsed positive voltage to the top electrode. This causes oxygen ions to migrate away from the tantalum oxide, raising the resistance and making the cell non-conductive. The simple structure of a

metal oxide stacked vertically between two electrodes results in excellent low power consumption and high-speed rewriting characteristics.

> These Panasonic 8-bit MCUs have a total of 64 kBytes of ReRAM. 62 kBytes is used in the program memory area and is used in a similar way to conventional Flash memory. 2 kBytes of ReRAM is used in the data memory area and is used in a similar manner to EE-PROM. ReRAM requires a write voltage of only 1.8V. Program Memory ReRAM has an endurance of 1K write cycles while ReRAM used as data memory is rated at up to 100K write cycles. Data retention is 10 years.

The Panasonic MN101L uses a simple 10 MHz 8-bit MCU core with a three-stage pipeline. It includes

a 16x16 multiply, 32/16 divide, Real Time Clock (RTC), ADC, and an LCD controller. The Panasonic MN101L Series Evalu-

ation Board, also available from Mouser Electronics, helps developers evaluate the MN101L and test Panasonic's new ReRAM technology.

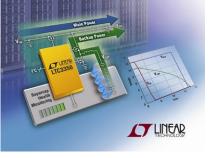

#### 10-A backup power controller manages supercapacitor stacks

TC3350 is a supercapacitor charger and backup controller IC that includes all of the features necessary to provide a complete, standalone capacitor-based backup power solution to provide short-term uninterrupted power in the event of a main power failure, for data backup for solid state drives (SSDs) and nonvolatile dual in-line memory modules (NVDIMMs), power fail alarms in medical and industrial applica-

tions, as well as a host of other "dying gasp" power fail indicators.

LTC3350 provides all PowerPath control, capacitor stack charging and balancing, and capacitor "health" monitoring to ensure that the backup system is capable of reliable operation. It features a wide 4.5V to 35V input voltage range and over 10A of charge/backup current capability. The device also provides balancing and overvoltage protection for a series stack

of one to four supercapacitors. The LTC3350's synchronous step-down controller drives N-channel MOSFETs for constant current/voltage charging of the capacitor stack at up to 5V per cell. In backup mode, the step-down converter runs in reverse

as a synchronous step-up DC/DC to deliver power from the supercapacitor stack to the system supply to be backed up.

The LTC3350 contains an accurate 14-bit analogue-to-digital converter (ADC), which continuously monitors input and output voltage and current. In addition, the internal measurement system monitors parameters associated with the backup capaci-

tors themselves, including capacitor stack voltage, capacitance and stack ESR (equivalent series resistance) to ensure adequate energy storage and power delivery during backup. By monitoring the actual capacitance of the backup supercapacitors, the LTC3350 provides longer capacitor life by enabling the system to set the capacitor voltage to a minimum value while ensuring the required backup energy is maintained. All system parameters and fault status can be monitored

via a two-wire  $I_2C$  interface, and alarm levels can be set to alert the system to a sudden change in any of these measured parameters.

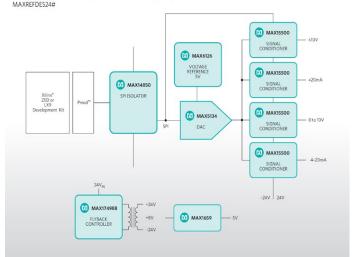

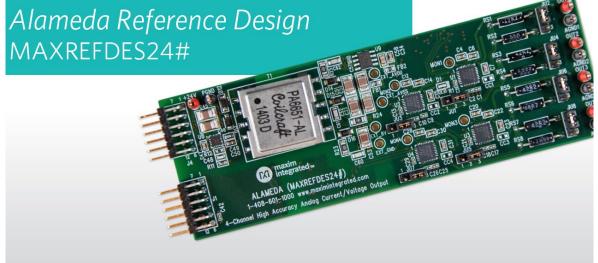

# Reference design outputs 4 analogue variables, cuts component count

sing one-third fewer components, this high-efficiency reference design from Maxim Integrated, the Alameda subsystem, is a flexible 4-channel bipolar analogue output module for industrial automation applications.

You can add a high-accuracy, 4-channel analogue output to an industrial automation designs with 33% fewer components than competitive designs, Maxim says; industrial programmable logic controllers (PLCs) need multiple, flexible, high accuracy analogue outputs. The Alameda subsystem combines four highaccuracy (<  $\pm$ 0.1%) outputs with a high-efficiency, low-noise power supply controller on a single board. Alameda offers great flexibility—its outputs are configurable to  $\pm$ 10V,  $\pm$ 20 mA, 0 to 10V, or 4–20 mA for current and voltage applications. Automatic error reporting for detecting open and short circuits, brownouts, and over-temperature conditions make this subsystem ideal for demanding, precision industrial control and automation applications.

#### The design...

- is fully tested: schematics, layout files, and firmware are available for immediate use and customisation.

uses fewer components: unique, integrated parts reduce number of components by 33% compared to competitive designs.

speeds designs: integrates an efficient power supply with a 4-channel analogue output in a single compact system to solve noise issues and save engineers development time.

- improves PLC system reliability: automatically detects shortcircuit, open-circuit, brown-out, and over-temperature conditions.

A second Reference Design from Maxim is aimed at gathering electricity distribution data faster and more accurately. The Petaluma reference design enables more intelligent grid data Alameda Reference Design: 4-Channel Analog Output

management with 3-phase, high-speed analogue data collection, yielding real-time measurements for utilities and infrastructure providers to simultaneously and accurately measure distributed power grid data.

Utility organisations worldwide, says Maxim, are deploying more robust applications that require highly accurate distributed grid status data to exploit distributed generation technologies such as solar and wind power. Voltage and current measurements must be gathered simultaneously for all lines, so the utility can understand the timing among phases and ensure maximum uptime across the grid. Petaluma is a high-speed, simultaneoussampling, 8-channel analogue input front-end (AFE) that monitors grid data simultaneously from all phases, so grid managers

can optimise their distribution automation signal chain.

Petaluma is tuned to the 50 Hz to 60 Hz signal to match power grids around the world. The simultaneous sampling of three phases is done with low power consumption in the 1W range. Its high-speed sample rate (250 ksamples/ sec per channel) comes with 16-bit accuracy, allowing for quick responses to grid fault conditions.

# 14-bit, 2 Gsample/sec converters boost performance, ease of use

nalog Devices has introduced two high speed analogueto-digital converters at 14-bits and 1 or 2 Gsamples/sec, that the company says are the best such parts for handling wide bandwidth signals, with wide dynamic range, while providing the linearity required for undersampling.

The parts feature a range of integrated functions to help you exploit their performance, and to simplify their use; the "break-through performance, bandwidth, and integrated functionality" will drive applications further towards direct-RF sampling, ADI asserts.

AD9680 is a dual-channel, 1.25-V,14-bit, 1-Gsample/sec A/D converter featuring the best noise and dynamic range performance in its class enabling the trend for direct RF sampling in communications, instrumentation and military/aerospace applications. Its noise density of -154 dBFs/Hz is the lowest in the industry. Wideband RF data acquisition allows for better signal extraction in congested RF environments, over a wider bandwidth; the device also features four digital down-converters to assist with isolating a specified fraction or subset of the overall bandwidth. The AD9680 is interoperable with FPGAs from major manufacturers and supported with known good configurations, and offers ease of interfacing.

The AD9680, ADI says, allows more degrees of freedom for system designers trading off signal bandwidth, noise and linearity because it can digitise a DC to 2-GHz input signal with an accompanying dynamic range performance that was previously unavailable on the open market. You can increase signal sensitivity and bandwidth data rate, while enabling the use of an advanced reconfigurable data acquisition or radio platform. The A/D converter is available with an evaluation board design environment and reference designs for rapid system prototyping and board-level design and layout.

The AD9680 was designed for sampling wide bandwidth analogue signals up to 2 GHz with best-available dynamic range and noise performance over its rated bandwidth range. When converting a 1-GHz input, the converter achieves spurious-free dynamic range (SFDR) performance of 80-dBc and 61.5-dBFS signal-to-noise ratio (SNR) while consuming 1.65 W of total

power per channel. 2-Gsample/sec data converter

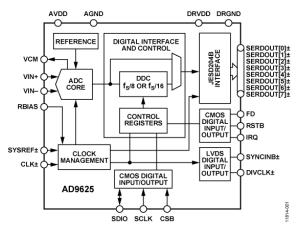

Also announced by ADI is the AD9625 that, "combines high bandwidth with industry-leading dynamic range and noise for first time in a 2-GSPS data converter to drive applications to direct RF sampling."

This part is a 12-bit, 2-Gsample/sec, AD9625 A/D converter. It provides the best noise and dynamic range performance in its class for better receiver sensitivity along with the ability to discern smaller signals in the presence of noise, clutter, blockers and interferers. This performance combined with 2-Gsample/ sec bandwidth and integrated signal processing functionality enables the trend to direct RF sampling in communications, instrumentation and military/aerospace applications. The converter's noise spectral density of 149.5 dBFS/Hz, coupled with high-input bandwidth, allow designers to use undersampling system architectures into the 2nd Nyquist zone, saving on a frequency down-conversion stage.

An ADI spokesman confirmed that the 9265 – a single channel part – is not a variant of the 9680, interleaving the two channels of the 9680, but is a completely separate design. It shares features with the 9680, in that it also has additional on-chip functionality for ease-of-use, such as digital-down-conversion to select a subset of the input bandwidth; and the JEDEC JESD204B interfacing capability.

The AD9625's wider input bandwidth enables advanced RF sampling architectures and allows designers to reduce the number of analogue frequency down-conversion stages and their associated noise and cost contributions. The simplified system architecture eliminates the need to interleave multiple A/D converters to obtain needed performance and allows for development of reconfigurable platforms. It is available with an evaluation board design environment and reference designs to simplify system prototyping and board-level design and layout.

The AD9625 achieves 80-dBc spurious-free dynamic range (SFDR) with a 1-GHz input. The AD9625 is, ADI claims, the only open-market-available 12-bit, 2-Gsample/sec, A/D converter that simplifies the digital interfacing challenge by integrating two digital-down converters (DDC), two numerically controlled oscillators (NCO) and a configurable JESD204B serial link for the output data.

Key applications include ultra-wideband RADAR, wideband front-ends for digital storage oscilloscopes and data acquisition platforms.

### HYBRID EXECUTION - THE NEXT STEP IN THE EVOLUTION OF HARDWARE-SOFTWARE CO-DEVELOPMENT

Software has become a crucial component as it determines significant portions of the functionality visible to us end consumers, as well as differentiation.

Over the past decade the software content to be addressed by semiconductor companies has multiplied several-fold. Where providing some core drivers and managing an ecosystem of operating system (OS) providers was sufficient in the late 90's to win a socket in the mobile space, today the contenders for providing an application processor have to be able to deliver the chip with multiple OSs already ported, up and running, ready to be adopted by system customers.

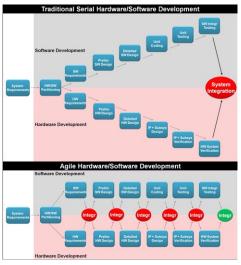

Unfortunately, in classic development flows, hardware and software – while ultimately derived from joint requirements – diverge in their development and in the worst case integration doesn't happen until a "big-bang" integration test is done.

The upper portion of Figure 1 shows such a disconnected hardware-software development flow from requirements through preliminary design, unit coding, testing and integration. The system integration at the very end often brings surprises that cannot be overcome without significant re-development. The industry has been striving for years to achieve a fully agile system development flow as indicated in the lower portion of Figure 1. Integration ideally should happen early and then be repeated often.

Given its importance, software has become the long tail in development cycles and its efficient development and testing is of great concern. Design teams are attempting to develop software as early as possible on whatever representation of the hardware they can get their hands on – achieving what the industry sometimes calls the great shift to the left. In an ideal world software development would be enabled at the very start of a chip-development project, but in reality users face various development options across levels of abstraction and different execution engines.

Hardware execution engines to enable early software devel-

**Figure 1.** The need for an agile hardware/ software development flow.

opment; Figure 2 illustrates the situation, outlining the various development engines that project teams consider using to bring hardware and software together as early as possible.

During a chip development project, verification and software development is mainly done on four different core execution engines.

Figure 2. There is no one-fits-all solution.

#### Virtual prototypes

Virtual prototypes are transaction-level representations of the hardware, able to execute the same code that will be loaded on the actual hardware, and often executing at well above 100 MIPS on x86-based hosts running Windows or Linux. To the software developer, virtual prototypes look just like the hardware because the registers are represented correctly, while functionality is accurate but abstracted. As an example, processor pipelines and bus arbitrations are not represented with full accuracy. While they can be made available to users early in the design flow, one of the challenges project teams need to consider is that modelling may take time and effort for which the return on investment (ROI) has to be considered carefully. Especially for designs that contain a large percentage of IPreuse, remodelling of existing RTL may be a non-feasible hurdle to take in cases for which an IP provider does not provide transaction-level models for the licensed IP. In addition, even if transaction-level models have been developed, keeping them synchronised with the actual implementation as it is undergoing changes, requires effort that often is not invested and leads to a situation that the initial models are no longer synchronised with the final implementation. As a result, for smaller designs virtual prototypes may not even be considered by project teams.

#### **RTL** simulation

Register transfer level (RTL) simulation executes the same hardware representation that is later fed into logic synthesis and implementation. This is the main vehicle for hardware verification and it executes in the Hertz range, but it is fully accurate as the RTL becomes the golden model for implementation, allowing detailed debug of the hardware. However, its limitations in speed make it infeasible for larger scale software development such as operating system (OS) bring-up. If at all used for software development, users will do smaller scale software development for drivers and lower layers of the software stack. Due to RTL being the "golden" description from which the implementation can be automatically derived using logic synthesis, RTL simulation is the minimum that project teams require for verification of the hardware.

The author continues with an outline of the alternative approaches of Emulation and FPGA prototyping, before looking at

the solutions that are emerging as "sweet spot" options for today' designs, and at progress towards an Agile hardware/software development environment. Click right.

# Analog Tips

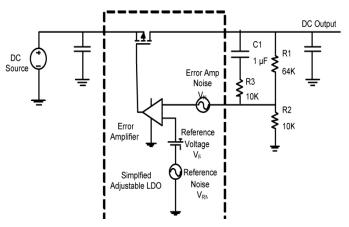

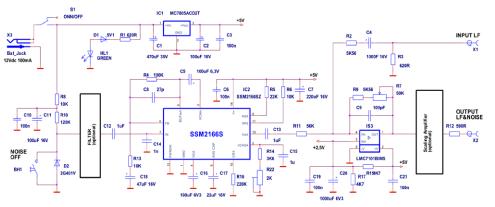

### SIMPLE RC NETWORK REDUCES LDO NOISE BY GLENN MORITA

oise is extremely important to designers of high-performance analogue circuits, especially high-speed clocks, analogue-to-digital converters, digital-to-analogue converters, voltage-controlled oscillators, and phase-locked loops. A low-dropout regulator (LDO) can power these circuits. A key to reducing LDO noise is keeping its noise gain close to unity.

The figure shows a simplified block diagram of a typical adjustable-output LDO. The output voltage,  $V_{OUT}$ , is the product of the reference voltage and the DC closed-loop gain of the error amplifier:  $V_{OUT} = V_R \times (1+R1/R2)$ , where (1+R1/R2) is the DC closed-loop gain of the error amplifier. The noise gain is equal to the DC closed-loop gain. Reducing the noise gain can reduce the output noise of adjustable-output LDOs where the feedback node is accessible.

Adding a simple RC network reduces the output noise while improving the power supply rejection and load transient response. The network formed by R3 and C1 reduces the AC gain of the error amplifier. To ensure stability with LDOs that have low phase margin or are not unity-gain stable, choose R3 to set the amplifier's high-frequency gain to approximately 1.1. To reduce noise in the 1/f region, choose C1 to set the low-frequency zero to less than 10 Hz. With the noise-reduction network, the AC gain is close to unity for much of the bandwidth, so the reference noise and error amplifier noise are amplified to a lesser degree.

With this network, the noise performance shows significant improvement between 20 Hz and 2 kHz. Above the zero created by R1 and C1, the noise characteristic with the noise-reduction network is nearly the same as it is at unity gain. Above 20 kHz, the closed-loop gain of the error amplifier meets the open-loop gain, so no further reduction in noise gain is possible.

The power supply rejection ratio (PSRR) over this frequency range also improves. The amount of improvement, in dB, is approximately 20×log(1+R1/R3) for frequencies below where the closed-loop gain and open-loop gain converge. The overall PSRR increases by about 17 dB from 100 Hz to 1 kHz. The improvement decreases until about 20 kHz where the open-loop gain and closed-loop gain converge.

The noise-reduction network also improves the LDO's transient load response. With the noise-reduction network, the LDO is able to respond to the load transient in less than 50  $\mu$ sec, as compared to 500  $\mu$ sec without the network.

One drawback to the noise-reduction network is that it increases the startup time, from about 600  $\mu$ sec to 6 msec with C1 = 10 nF and 600 msec with C1 = 1  $\mu$ F. This should not be an issue

**Figure 1.** Simplified adjustable LDO block diagram shows internal noise sources.

for applications that do not switch the LDO off and on once the circuit is fully powered.

This technique will work with LDOs with architectures similar to that shown in the figure, where both the reference voltage noise and the error amplifier noise are amplified by the DC closed-loop gain. LDOs such as the ADP125, ADP171, ADP1741, ADP1753, ADP1755, ADP7102, ADP7104, and ADP7105 all share this general architecture and will benefit greatly from the use of a noise-reduction network.

Newer, ultralow-noise LDOs such as the ADM7151 will not benefit from the noise-reduction network because the architecture uses the LDO error amplifier in unity gain, so the reference voltage is equal to the output voltage. In addition, the internal reference filter has a pole below 1 Hz, heavily filtering the reference voltage and virtually eliminating any reference noise contribution.

#### References

**Morita, Glenn.** "Low Dropout Regulators—Why the Choice of Bypass Capacitor Matters." Analog Dialogue, Volume 45, Number 1, 2011.

Morita, Glenn. AN-1120 Application Note. Noise Sources in Low Dropout (LDO) Regulators. Analog Devices, Inc., 2011.

**Glenn Morita** [glenn.morita@analog.com] is an applications engineer with ADI's Power Management Products Team in Bellevue, Washington.

#### **CABE ATWELL**

### TOP FREE DIY TOOLS EVERY ENGINEER NEEDS

very electrical engineer who does DIY projects knows that dozens of free resistor calculators are out there that can save quite a bit of tedious work. Other simple tools can be found, but traditionally the free tool arsenal would stop there. Sure, there are base platforms such as SolidWorks and Autodesk, but what happens when they are missing a feature needed at that exact moment?

Now we're seeing a relative explosion in free tools for engineering electronics. It is easy just to hit the Net and use the myriad resources available. Some of those online tools prove to be worthless, and it's back to blind searching or some paid tool, but free software extends far beyond the functionality of a simple calculator.

To help sort out the nonsense from the useful online tools, check out the list in Figure 1.

#### Calculatoredge: when one calculator isn't enough

One of the more useful tools in an engineer's toolbox is a physical calculator. Why does it seem to get lost when it's truly needed? Workstations usually save the day. Those included in your OS of choice (Windows, iOS, Linux, etc.) are good for simple tasks but not so great for other things, even in scientific mode.

Searching for the right one online will net you roughly 131 million choices. Which one are you to choose when there are so many? Why not choose them all?

Almost all calculator versions known to humankind are located in one convenient site, Calculatoredge. It boasts no fewer than a few hundred calculators for just about every field imaginable (and perhaps some that are unimaginable), including electrical, mechanical, civil, chemical, and even math. There's no need to search aimlessly for that obscure number cruncher ever again. Some of the more complex calculators even come with some rudimentary instructions.

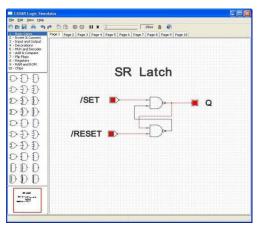

#### Cedar Logic Simulator on SourceForge

When it's time to test simple digital logic gates and registers or even some high-level components, you can turn to Cedar

#### Calculatoredge

| GENERAL          | CIVIL                                    | OPTICAL                         | MECHAN    | VICAL                                   | PLASTICS                             | METALLURGY |  |

|------------------|------------------------------------------|---------------------------------|-----------|-----------------------------------------|--------------------------------------|------------|--|

| ELECTRICAL       | ELECTRONICS                              | CHEMICAL                        | PHYS      | tcs                                     | CERAMICS                             | OIL & GAS  |  |

| STRUCTURAL       | FINANCE                                  | CE CHARTS MATH                  |           | H                                       | BOOKS STORE                          | JOB PORTAL |  |

|                  |                                          | ELECTRONIC                      | S ENGINEE | RING                                    |                                      |            |  |

| Pressure         | Se                                       | Speed-Distance-Time             |           | Voltage-Current Resistance-Power        |                                      |            |  |

| Ohm's Law        |                                          | PI Attenuator                   |           | Capacitance-Frequency-Inductance        |                                      |            |  |

| Mass Length      |                                          | Voltage Drop                    |           | Resistance-Frequency-Capacitance        |                                      |            |  |

| Temperature      | PCI                                      | PCB Circuit Trace Width         |           | Resistance Color Code Value             |                                      |            |  |

| Velocity Of Sour | nd Laser F                               | Laser Real-Time Unit Converter  |           | Pressure ranges of Vacuum Pumps         |                                      |            |  |

| RMS Value        |                                          | TEE Attenuator                  |           | Capacitor Energy and Time Constant      |                                      |            |  |

| Wheatstone Brid  | ge Air Co                                | Air Core Inductor Inductance    |           | Flyback Transformer Power Supply        |                                      |            |  |

| Parallel Resist  | Standa                                   | Standard Resistor Closest Value |           | BJT Transistor Bias Voltage             |                                      |            |  |

| L-C Resonance    | e Frequ                                  | Frequency and Wavelength        |           | Non-Inverting Op-Amp Resistor           |                                      |            |  |

| LED Resistor     | Ma                                       | Maximum Flux Density            |           | Capacitor Parallel Plate Capacitance    |                                      |            |  |

| Microstrip Induc | tor MSI                                  | MSP430 UART Register            |           | A - S - Y - Z Parameter Conversion      |                                      |            |  |

| Reactance Calcul | ators He                                 | Heat Sink Temperature           |           | Butterworth Tee Low Pass Filter         |                                      |            |  |

| Skin Effect      | Induc                                    | Inductance of Straight Wire     |           | Butterworth Tee High Pass Filter        |                                      |            |  |

| RF Amplifier     | Inver                                    | Inverting Op-Amp Resistor       |           | Chebyshev Tee Low Pass Filter           |                                      |            |  |

| Whip Antenna     | () () () () () () () () () () () () () ( | Helical Antenna                 |           | Chebyshev Tee High Pass Filter          |                                      |            |  |

| Voltage Divide   | Butten                                   | Butterworth Pi Low Pass Filter  |           | Equal Component Low Pass Filter         |                                      |            |  |

| Wire Paramete    | Butters                                  | Butterworth Pi High Pass Filter |           | Equal Component High Pass Filter        |                                      |            |  |

| Pinhole Sizing   | Cheby                                    | Chebyshev Pi Low Pass Filter    |           | Sallen-Key Butterworth Low Pass Filter  |                                      |            |  |

| Fris Path Loss   | Cheby                                    | Chebyshev Pi High Pass Filter   |           | Sallen-Key Butterworth High Pass Filter |                                      |            |  |

| IC 555 Timer     |                                          | Single Layer Coil               |           | Polyester Capacitor Color Code          |                                      |            |  |

| HF Filter        | 0                                        | Decibel Calculators             |           | Efficiency Bandwidth Product            |                                      |            |  |

| Zener Diode      |                                          | RF Power Density                |           | Subwoofer Box Tuning Frequency          |                                      |            |  |

| Line Of Sight    | Sul                                      | Subwoofer Vent Length           |           |                                         | Vented Ported Subwoofer Box          |            |  |

| Battery Life     | Ra                                       | Radar Range Equation            |           |                                         | Subwoofer Vent Minimum Port Diameter |            |  |

Figure 1. Calculator choices from Calculatoredge: this is only the "Electronic Engineering" panel.

Logic Simulator (still in beta edition). hosted on Source-Forge, for some free online simulations. Designing circuits is great and all, but will they function correctly and perform when it counts? The Cedar Logic Simulator allows users to perform test simulations at the transistor. register/transfer, gate, and other levels.

The software also can be used as an introductory tool for teaching logic design and an entry platform for circuit design by allowing users to

drag and drop gates, inversions, and connections. There are also options for undo/redo and copy/paste functions. Projects can even be exported to monochrome or colour bitmap files for project integration. SourceForge's main application window allows users to move

Figure 2. Cedar Logic Simulator, on SourceForge

back and forth through 10 different pages for multiple projects, making it one of the better free applications on the Web.

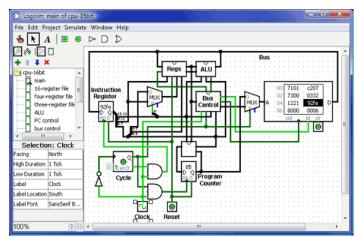

#### Logisim 2.7.0, an alternative to Cedar Logic Simulator

The Cedar Logic Simulator isn't the only free simulation tool available on the Internet. Tools that rival its design and simulation applications include Carl Burch's Logisim logic simulator. Students of the computer sciences often use the app as an introductory circuit design/learning tool, but it's practical for use outside the classroom, as well.

Logisim incorporates some of the same features as Cedar, including design and simulation platforms with preconfigured elements: AND, OR, NOT, etc. However, the software provides more in-depth functionality, including a tool for drawing colour-coded wiring connections that make programming and debugging a little easier. One of the more interesting aspects of Logisim is that it's portable and can be stored on removable storage media. It also can be used on any Windows-based PC, and it runs immediately after you click on the program. That's a luxury in today's install-but-with-malware world.

Click right for Carl's continuation of this article, in which he looks at circuit simulators, CAD packages for schematic capture, PCB layout, 2D and 3D design, and even free CNC machine control.

Complete article, here

Figure 3. A screenshot from Logisim 2.7.0.

#### PETER BLYTH, XP POWER

# UNDERSTANDING EFFICIENCY: LOOKING FOR THE WORST-CASE SCENARIO

t's standard practice to put the best-case scenario on data sheets, but how does that differ from the efficiency that can actually be achieved in your application?

Efficiency is one of the key parameters to consider when selecting the correct switch mode power supply. Pressure on equipment designer to deliver more functionality in a small size can result in more power being required which has a direct effect on the form factor of the power supply. The consequence of this is power supplies now have to deliver more output power in a smaller form factor. This, coupled with the need to meet more demanding environmental legislation and to minimise or eliminate fan cooling, is forcing equipment designers to look for more efficient power supplies.

An efficient power supply means less power is wasted as heat, which is the biggest factor in reliability of electronic components. Efficiency therefore has a big effect on the reliability and lifetime of the end equipment. Selecting an efficient power supply may also mean the equipment can be designed for operation without a cooling fan, reducing the audible noise, which is very desirable in many applications.

When deciding on a particular power supply for a piece of equipment, the minimum efficiency required for the equipment to run without a cooling fan, or with a certain lifetime guaranteed, may be calculated. The designer then turns to power supply data sheets to decide whether a particular supply meets those minimum efficiency criteria. small size<br/>direct ef-<br/>sequence<br/>utput power<br/>to meetFactors affecting efficiency<br/>Efficiency is calculated as the output power divided by the input<br/>power, and is usually expressed as a percentage. The difference<br/>between the input power and output power is the power wasted<br/>in the power supply as heat.

The input power is the product of the input voltage, current and power factor. If the input voltage (ie. mains voltage) is lower, to supply the same output power the current will have to increase, resulting in greater losses in the power components. The losses in the inductors and transformers are I<sub>2</sub>R, where R is the resistance of the component. For the same efficiency, halving the input voltage results in twice the input current. In reality the input current is more than double due to the reduction in efficiency caused by increased power losses, resulting in more

product may be selected on headline efficiency alone, perhaps

operating conditions, a cooling fan is needed or a higher power output supply must be used deliver the performance required.

Incorrect selection will result in increased cost, which is why it's

at an attractive cost level, only to find that at the worst-case

vital to work with worst-case efficiencies from day one.

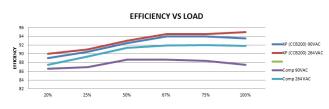

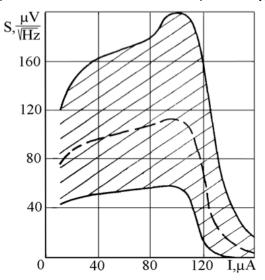

**Figure 1-** Power supply efficiency over variable load conditions, with different supply voltages. Curves for the XP CCB200 and a comparable supply from another manufacturer are shown.

Equipment designers should

be aware that the efficiency figure quoted on the manufacturer's website or data sheets is almost certainly a best-case scenario. The headline efficiency found on marketing material is true only when the power supply is run under favourable, or indeed, optimum, conditions. The actual conditions the power supply will experience be used in could be very different.

For example, it's common for the same model of industrial and medical equipment to be sold worldwide. Even if a power supply states it has a 'Universal Input', that doesn't guarantee its efficiency matches the headline efficiency for all inputs. The efficiency at the highest input voltage, European mains at 230 VAC, will be different to the efficiency the power supply can achieve at the lowest input voltage, Japanese mains at around 100 VAC or 115 VAC in North America.

The power supply's efficiency, when it's working under the most challenging set of operating conditions, may be thought of as the worst-case efficiency. This worst-case efficiency can be calculated by digging deep into the product's specification, which is essential to ensure the correct product is selected. A than quadrupling the power loss of some of the components within the power supply and more than doubling the losses in others.

The same phenomenon exists for the output power, calculated as the product of the output current and output voltage. The optimum output voltage is the highest the PSU can supply; at lower output voltages, currents increase, and some losses increase proportional to the square of the current.

As an example, a comparison between the efficiency of the XP CCB200 at 264 and 90V, and that of a comparable AC-DC power supply from another manufacturer is shown in Figure 1. The different curves show the efficiency at the lowest possible input voltage (Japanese mains minus 10%), and the highest (UK mains plus 10%). With the two different input voltages, the efficiency of the XP CCB200 varies 1-2%, whereas the other power supply's efficiency drops almost 5 percentage points at full load when switching to the lowest input voltages. Putting this in terms of wasted power, the XP product would dissipate 2W to 4W more power at the lower input voltage, whereas the power supply from the other manufacturer would dissipate nearly 10W more power. This device's headline efficiency is 92%, but by switching to Japanese/North American voltages, the maximum efficiency it can achieve is 88.5%, and then only under specific load conditions.

In the continuation of this article, the author notes the effects on efficiency of additional parameters, and of power supply topology – click here.

#### NAZAFAT ULLAH KHAN

# **BANDPASS FILTER, ADJUSTABLE Q, CONSTANT MAXIMUM GAIN WITH TWO OP-AMPS**

Equation (1) expresses the second-order bandpass transfer function of a BPF:

$$H_{BP}(s) = K \frac{\frac{s}{\omega_0}}{\left(\frac{s}{\omega_0}\right)^2 + \frac{1}{Q} \left(\frac{s}{\omega_0}\right) + 1},$$

(1)

Where K represents constant filter's gain, Q represents the filter's quality factor.

In article by H. Martínez et al. (Ref. [1]) they describe a BPF with adjustable quality factor and constant transfer coefficient at the resonant frequency designed with three op-amps. The transfer function of this BPF corresponds to expression (1), in which K is inversely proportional to quality factor Q. This bandpass filter with an adjustable quality factor (Reference 1, Figure 1) comprises a twin T cell and a differential stage.

This design discussed here allows us to exclude the differential stage from the scheme of BPF. Properties of the scheme offered by H. Martinez et al. all remain.

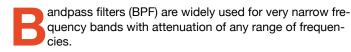

The block diagram of the BPF shown in Figure 1a, shows a voltage-follower using IC1 and IC2, may be implemented using a standard dual operational amplifier by connecting its inverting inputs to the op-amp outputs.

The BPF (Figure 1) is based on a Twin-T configuration (Figure 1b).

**Figure 1-** Scheme of active BPF (a) provides a change in quality factor, while maintaining constancy of the gain coefficient at a resonant frequency based on twin T cell (b) The Twin T cell without the differential amplifier.

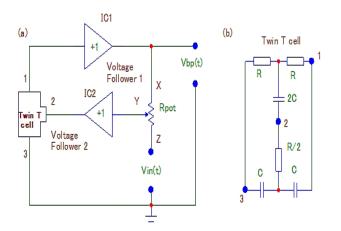

**Figure 2-** Magnitude and phase Bode plots at the BPF output, VOUT(t), show effects of varying twin-T-cell positive feedback factor, m, from 0.1 to 0.9.

The gain function of the offered filter according to (Reference 1, Equation 2) has the form:

$$H_{BP}(s) = \frac{V_{BP}(s)}{V_{IV}(s)} = \frac{4RC(1-m)s}{(RCs)^2 + 4RC(1-m)s + 1}.$$

(2)

where m is the frequency-independent coefficient of positive feedback supplied to the twin T cell (Figure 1b). The quality factor's value depends on the potentiometer,  $R_{POT}$ , position. At the bottom position of the potentiometer the cursor shows the filter's quality factor Q at a minimum, and when moving the potentiometer up in position, the quality factor increases.

The positive feedback factor m is defined as:

$$m = \frac{R_{\rm YZ}}{R_{\rm XZ} + R_{\rm YZ}} = \frac{R_{\rm YZ}}{R_{\rm FOT}}.$$

(3)

The resonance frequency of active filter is:

$$\omega_0 = 2\pi f_0 = \frac{1}{RC}.$$

(4)

The quality factor Q from Equation 2 is:

$$Q = \frac{1}{4(1-m)}.$$

(5)

Following H. Martinez et al. [1], the maximum gain, AMAX, at  $\omega = \omega_0$ , always remains constant and equal to 1 (0 dB) and is independent from Q. The minimum quality factor is 1/4 for m=0, which corresponds to the potentiometer's rotor connected to

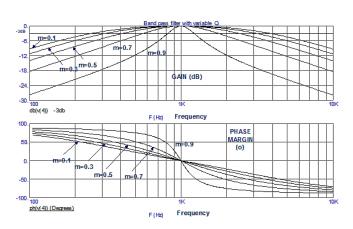

**Figure 3-** Two schemes , which have identical transfer function. (a) - scheme offered by Martinez et al.; (b) - scheme of our design idea.

the input. The maximum gain is theoretically infinite, but, practically, it's difficult to achieve a quality factor beyond 50. In typical applications Q variations are from 1 to 10.

Figure 2 shows Bode plots for the BPF's output, VBP(s)/VIN(s), for values of m from 0.1 to 0.9. In the graph, frequency f0 equals to 1 kHz. Modelling of the filter was done using a circuit simulation program by (ECAD) Micro-CAP 9 of "Spectrum Soft".

Our scheme is obtained by a topological transformation [2] of the original scheme of the notch filter of IC1 and IC2, by transferring the ground wire on the input voltage source Vin (t).

Thus, the proposed circuit excludes additional differentiating stage IC3 (Figure 3b) and achieved similar results as Martinez et al (Figure 3a).

#### References

1. Martínez, Herminio et al., "Bandpass filter features adjustable Q and constant maximum gain", EDN, March 3, 2005, p. 71–72.

2. Belov A.V., "Methods for the conversion of electrical circuits on the basic of nullors". Journal "Izvestiya vysshih uchebnyh zavedeniy Rossii. Radioelektronika", 2012, №. 2, p.30-37. LETI, Saint-Petersburg.

Editor's note: This article was written at the Institute of Experimental Medicine of the North-West Branch of the Russian Academy of Medical Sciences (IEM NWB RAMS) Saint–Petersburg, Russia

# **DESIGNING FOR IOT—PART IV—THE CLOUD**

n this last segment of this series, we will look at back-end services. Some IoT systems may not need back end services like a smartphone controlling a TV, but the majority of the currently envisioned IoT systems reply on the collection, processing and usage of data by the IoT devices and for this, some form of Information Technology different than embedded systems is required.

This article is the conclusion to a four-part series:

- In Part 1, we reviewed the choices facing an embedded developer who needs to build wireless networking into an IoT device (that is, the Thing in the Internet of Things).

- In Part 2, we discussed the different type of IoT devices, and the design choices that you face when designing the hard-ware and software architectures.

- In Part 3, we looked at the Internet itself, how IoT devices make use of it.

#### The Cloud

The Cloud: This is another interesting buzzword. When I was Director of Engineering at Teleglobe Canada, every time we sat in a meeting room to design a network, we drew it as a cloud. A network is a cloud. The Internet is a cloud. And cloud computing is nothing more than an array of networked computers that allow you to offload processing tasks from your embedded system. The same is true for

data storage: why store data locally, when you can store it in a secured data centre, with guaranteed power and back-ups?

There is, of course, one fundamental assumption in cloud computing: The network is always available!

So "cloud computing" is a term coined to put a simple name on something that has become very complex. Many companies have launched services that try their best to hide this complexity; these include Apple's iCloud, Google Cloud Platform, Microsoft SkyDrive, and others. These Cloud computing/storage systems are intended for use with desktop and mobile personal computers. Embedded developers need something similar for IoT devices.

Industry analysts are forecasting the creation of billions of IoT devices by 2020, and these devices will produce huge amounts of data. There are a few approaches for managing and processing all this data.

I see two trends developing among companies that are moving into IoT:

- Some companies are developing and selling their own proprietary solutions because they feel they have the lead, and want to leverage it to its maximum.

- Other companies don't have the capability to deploy a complete infrastructure, and so prefer to rely on emerging public or commercial solutions.

You can define your own IoT from end-to-end. Many large companies are trying to do just that, and want to capture a good portion of this emergent market. Others are specialising in certain parts, such as GE with its Predix platform for the data

analytics of the industrial internet. Does it mean you absolutely need to buy the provider cloud service stuff? No, you can probably build your own or outsource the expertise you don't want to build.

Running a backend service must become a core competency for any company attempting to do so; there will be no room for dilettantes. But not all organisations have the DNA to put in place a server farm, guarantee the fail-safe operation of their network, and guarantee data back-ups, system redundancy, and all the crucial things that come with it. Can your system cope with a network failure? If so, for how long?

Early IoT deployment has revolved around sensors and actuators connected to the public Internet via a gateway or hub, and delivering data to an Internet-based server (cloud computing). This is often a vertical integration built around one primary vendor (such as your utility provider and/or telecommunica-

tion carrier). All these providers have little or no interest in working together, resulting in an unmanageable melting-pot of services.

The army of devices that compose the Internet of Things will generate more data than any individual Web application. IBM's chief executive, Virginia Rometty, in The Economist blog "The World in 2014", provides IBM's estimates on the quantity of data to be processed in

years to come: "By one estimate, there will be 5,200 Gigabytes of data for every human on the planet by 2020."

In his TED talk: The Internet of Things is Just Getting Started [Reference 1], Arlen Nipper calculates that to support the 30 billion connected devices expected to arrive by 2020, we would need to deploy about 340 application servers per day (120,000 servers per year), assuming that we want to deploy all these systems as segregated applications. Mr. Nipper suggests that one way to make IoT possible in the coming years will be to adopt cloud computing.

Around the year 2000, all the telecom carriers claimed that they could each provide the Internet all by themselves. They invested billions of dollars into equipment purchases. Everybody was looking for the "killer application," the application that would create the "gazillions" of bytes of traffic to fill these networks. At that time, the application that was generating most of the network traffic was e-mail. Today, social media and video sharing are replacing e-mails. When the forecasted traffic did not materialise on this huge IP network, it triggered the dot-com bubble burst.

With IoT, we are finally seeing a new "killer application." When billions of devices exchange information over the Internet, they will require significant network bandwidth, and especially enormous data storage and processing capabilities. A new term has been coined lately to represent this new trend: Big Data.

In the continuation of this article, the author looks at backend services, and the contention that "every company will become a software company" - click right.

## ENSURING DIGITAL DISPLAYS FLOURISH IN ALL CONDITIONS

oday, wherever we go, information is at our fingertips – whether it comes from indoor equipment, outdoor kiosks, or the smartphone in our pocket. This penetration depends heavily on the equipment and devices' display and touch interfaces; can these UIs effectively deliver an engaging and reliable experience, withstanding challenges from any environment they find themselves in?

Below, we look at these challenges and the technologies to counter them. We then draw on **andersDX's** extensive experience with supplying UIs into widely varied applications to show these technologies working in practice.

### Display enhancement requirements and solutions

Display enhancements are typically needed to accommodate and compensate for glare and sunlight, fingerprints and scratches, shock, vibration and malicious attack, and temperature extremes. Additionally, as displays become increasingly interactive, any enhancements must be complemented by suitable touch screen solutions. Other issues including humidity, water and dust ingress can be solved with suitable, and wellestablished, enclosure designs.

Circular Polarisers provide optimal sunlight readability, cutting total light reflections to 1% of incident light. Sunlight readability can also be improved by applying anti-reflection optical films or coatings combined with optically-clear glue between the display's surface and the transparent protective layer. This can yield further reductions in total reflections to as low as 0.2%, resulting in a perceived increase in display contrast of some 300%. Anti-glare films reduce glare that can originate from over-head lighting, for example, by diffusing concentrated beams of light to levels far less distracting to the user, while increasing light output of a display's backlight unit to deliver a front of display luminance of around 1000nits or above, which will greatly contribute to improved sunlight readability.

| Challenge             | Solution                     | Comment                              |  |

|-----------------------|------------------------------|--------------------------------------|--|

| Readability in bright | Optical bonding              | Contrast up to 10:1, 300%            |  |

| sunlight and glare    |                              | improvement in impact resistance     |  |

|                       | Polariser                    | Cuts total light reflection to 1% of |  |

|                       |                              | incident light                       |  |

|                       | Anti-reflection optical film | Increases contrast ratio up to 300%  |  |

|                       | Anti-glare film              | Improves contrast ratio, reduced     |  |

|                       | -                            | surface reflections                  |  |

|                       | LED backlight                | 3 x increased light output           |  |

| Impact resistance     | Optical bonding              | See above                            |  |

|                       | Safety glass                 | Excellent for vandal resistance      |  |

|                       | Anti-smudge screens          | Reduce fingerprints and scratches    |  |

| Privacy               | Privacy filter               | Limits viewing angle to 48° or 60°   |  |

| Overheating in strong | Heat mirror                  | Rejects up to 90% of incident solar  |  |

| sunlight              |                              | energy                               |  |

| Extreme cold          | Transparent heater           | Extends operating temperature down   |  |

| environment           | _                            | to -50°C                             |  |

| Touch technologies    | Resistive                    | Early technology, still highly       |  |

|                       |                              | favoured in industrial applications  |  |

|                       | Projected capacitive         | Provides good user experience,       |  |

|                       |                              | popularity accelerated by use in     |  |

|                       |                              | smart devices                        |  |

|                       | Shadowsense                  | More recent technology, highly       |  |

|                       |                              | accurate and cost-effective          |  |

Table 1 summarises the UI challenges and enhancement solutions available.

Optical bonding, the term that describes the clear-gluing process mentioned above, is highly effective in outdoor and public environments. As well as improving contrast ratios to 10:1, it provides up to three-times better impact resistance. Safety glass is also available to provide an excellent level of vandal resistance, while anti-smudge screens reduce everyday fingerprint and scratching issues. For applications such as ATMs where privacy is required, privacy filters are available that limit full-field viewing angles to 48° or 60°.

Where strong sunlight creates heating as well as readability problems, a heat mirror can keep displays cool. By reflecting infrared radiation, these can reject 90% of incident solar energy. Conversely, a transparent heater can be used to warm displays in extremely cold environments, extending operating temperatures down to  $-50^{\circ}$ C.

Different touch technologies are available for interactive UIs. Resistive touchscreens are preferred where low cost and low emissions take precedence over ease of use. 4-wire types are standard, with 5, 6 and 10-wire solutions available as alternatives for enhanced robustness. They can be integrated with a coverlens for aesthetics and protection. PCAP Projected Capacitive touchscreens offer greater accuracy and an "iPadlike" user experience together with thinness, low weight, great durability, and multitouch capability. A recently-introduced technology – ShadowSense – offers a scalable and robust solution with drift-free performance, outstanding optical clarity and a fast, accurate response time. This optical touch technology, implementing multitouch detection from the periphery of the display, is reliable, durable and attractively-priced.

#### **Real-world display enhancement examples**

Because real-world applications are so diverse, finding the right UI products and engineering them into their target system takes innovation and flexibility. For example, an indoor environment is not necessarily benign; a recent UI project concerned a professional catering oven subject to the heat,

humidity and rough handling of a busy kitchen. Read more about the engineered solution, and others - click right.

#### **MECHATRONICS INDESIGN** FRESH IDEAS ON INTEGRATING MECHANICAL SYSTEMS, ELECTRONICS, CONTROL SYSTEMS, AND SOFTWARE IN DESIGN

# Control, control, you must learn control!

**Kevin Craig**

ver 20 years ago, while teaching at Rensselaer Polytechnic Institute, my colleagues and I, working in the emerging field of Mechatronics, came to understand the importance of integrating control in the design process from the very start of the design process.

Adopting a model-based design approach made this integration easy indeed, accessible to all engineers with some education in control fundamentals and their application to real engineering systems. The increase in the power of microelectronics

and the decrease in their cost has now made possible, in everyday systems, the application of control approaches found only in research labs a few years ago. Yes, now control is an indispensable technology in modern multidisciplinary engineering practice.

Alas, you would not come to that conclusion reviewing the engineering curricula at universities or speaking with most practicing engineers today who are products of those programs. Modelling and control make physics and mathematics relevant and necessary for the engineering student and this message needs to be delivered on day one. Why is this not so? If you have an answer, please let me know.

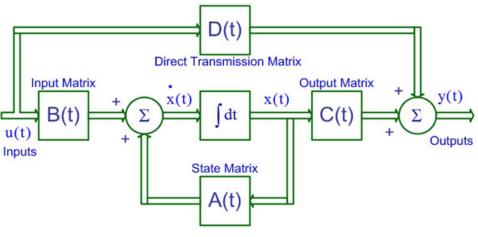

Classical Control Theory (root-locus and frequency response analysis and design, i.e., transform methods) is applicable to linear, time-invariant, single-input, single-output (SISO) systems. This is a complex frequency-domain approach. The transfer function relates the input to output and does not show internal system behaviour.

Modern Control Theory (state-space analysis and design) is applicable to linear or nonlinear, time-varying or time-invariant, multiple-input, multiple-output systems. This is a time-domain approach. This state-space system description provides a complete internal description of the system, including the flow of internal energy.

The aim of both techniques is to find a controller that satisfies the design specifications. Knowledge of both approaches, modern and classical, is essential to produce the best designs.

Even when control is taught, the subject of state variables